Flip-flop è un termine che rientra nell'elettronica digitale ed è un componente elettronico utilizzato per memorizzare un singolo bit di informazione.

Rappresentazione schematica del Flip Flop

- Poiché Flip Flop è un circuito sequenziale, il suo ingresso è basato su due parametri, uno è l'ingresso corrente e l'altro è l'uscita dallo stato precedente.

- Ha due uscite, entrambe sono complementari l'una all'altra.

- Può trovarsi in uno dei due stati stabili, 0 o 1.

Schema base del Flip Flop

Cos'è il T Flip Flop?

- Il flip flop T o per essere precisi è noto come Toggle Flip Flop perché è in grado di alternare il suo output a seconda dell'input.

- T qui sta per Attiva/disattiva .

- Toggle indica fondamentalmente che il bit verrà invertito, ovvero da 1 a 0 o da 0 a 1.

- Qui viene fornito un impulso di clock per far funzionare questo flop, quindi è un flip-flop con clock.

Costruzione del Flip Flop T

Possiamo costruire il T flip in tre modi e cioè:

- Utilizzando le infradito SR.

- Utilizzando le infradito D.

- Utilizzando le infradito JK

Modi per costruire T Flip Flop

Vediamo la costruzione del T Flip Flop utilizzando i Flip Flop SR, che richiedono 2 porte AND e 2 porte NOR come mostrato di seguito:

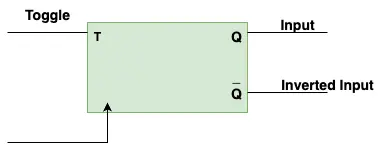

Schema a blocchi di base del T Flip Flop

Qui il diagramma a blocchi contiene gli ingressi Toggle e clock, Q e Q' sono gli ingressi complementari.

Funzionamento del T Flip Flop

Caso 1 : Diciamo, T = 0 e l'impulso dell'orologio è alto cioè 1, quindi l'uscita di entrambi, AND gate 1, AND gate 2 sarà 0 , cancello 3 l'uscita sarà Q e allo stesso modo cancello 4 l'uscita sarà Q' quindi entrambi i valori di Q e Q' sono uguali al loro valore precedente, il che significa Mantieni lo stato .

Caso 2 : Diciamo, T=1 , quindi l'uscita di entrambe le porte AND 1 sarà (T * orologio * Q) , e poiché T e clock sono entrambi 1, lo sarà l'uscita della porta AND 1 Q , e allo stesso modo l'uscita della porta AND 2 sarà (T * orologio * Q’) i.e, Q' . Ora, l'uscita del gate 3 sarà (Q’+Q)’ e diciamo che Q' è zero, lo sarà l'uscita del gate 3 (0+Q)’ che significa Q' e allo stesso modo lo sarà l'uscita del gate 4 (Q+Q’)’ e poiché Q' è zero, l'uscita del gate 4 sarà Q', il che significa 0 poiché Q’ è zero. Quindi in questo caso possiamo dire che l'output si attiva/disattiva, perché T=1 .

Tabella della verità di T Flip Flop

- Qui, T è l'ingresso Toggle, Q è l'ingresso dello stato presente, Qt+1 è l'uscita dello stato successivo.

- Da qui possiamo vedere che, ogni volta che Toggle (T) è 0, l'uscita dello stato successivo (Qt+1) è uguale all'ingresso dello stato corrente (Q).

- Ogni volta che Toggle (T) è 1, l'output dello stato successivo (Qt+1) sarà complementare all'input dello stato corrente (Q), il che significa che verrà attivato/disattivato.

Equazione caratteristica

- L'equazione caratteristica ci dice quale sarà il prossimo stato del flip flop in termini di stato attuale.

- Per ottenere l'equazione caratteristica, viene costruita la K-Map che verrà mostrata come di seguito:

- Se risolviamo la K-Map sopra, l'equazione caratteristica sarà Q(n+1) = TQn’ + T’Qn = T XOR Qn

Tabella di eccitazione

La tabella di eccitazione racconta fondamentalmente l'eccitazione richiesta dal flip flop per passare dallo stato corrente allo stato successivo.

- Qui, ogni volta che T è 0, Qt+1 è uguale all'input Q.

- E, ogni volta che T è 1, Qt+1 è complementare all'input Q.

Applicazioni di T Flip Flop

Esistono numerose applicazioni di T Flip Flop nel sistema digitale, che sono elencate di seguito:

- Contatori : T Infradito utilizzate nei contatori. I contatori contano il numero di eventi che si verificano in un sistema digitale.

- Archivio dati : T Infradito utilizzati per creare memoria utilizzata per archiviare dati quando l'alimentazione è spenta.

- Circuiti logici sincroni : I flip-flop T possono essere utilizzati per implementare circuiti logici sincroni, ovvero circuiti che eseguono operazioni su dati binari in base a un segnale di clock. Sincronizzando le operazioni del circuito logico con il segnale di clock utilizzando i flip-flop T, il comportamento del circuito può essere reso prevedibile e affidabile.

- Divisione di frequenza : Viene utilizzato per dividere la frequenza di un segnale di clock per 2. Il flip-flop attiverà la sua uscita ogni volta che il segnale di clock passa da alto a basso o da basso ad alto, dividendo quindi la frequenza di clock per 2.

- Registri a scorrimento : I flip-flop T possono essere utilizzati nei registri a scorrimento utilizzati per spostare i dati binari in una direzione.

Conclusione

In questo articolo partiamo dalle basi delle infradito, cosa sono in realtà le infradito e poi abbiamo discusso delle T Flip Flop, tre modi in cui possiamo costruire le T Flip Flop, il diagramma a blocchi di base, il funzionamento delle T Flip Flop , è la tabella della verità, l'equazione caratteristica e la tabella di eccitazione e alla fine abbiamo discusso le applicazioni delle infradito a T.